#### **VXI**bus

# **UP TO 12 CHANNELS of 3-WIRE LVDT/RVDT STIMULUS** ON-BOARD PROGRAMMABLE EXCITATION SUPPLY

## **FEATURES**

- Programmable output voltage

- On-board optional programmable excitation

- Continuous background BIT testing

- Extensive diagnostics

- Wideband 360 Hz to 20 kHz

- Optional Ratiometric or Self leveling conversion

- Message based C size VXI card for with Mate CIIL VISA Plug-and-Play Driver Library available.

- Dynamic address configuration

- VXIbus data rate of 2 megabytes/sec

- Data is processed within 100 us

- Occupies only a single slot

- No adjustments or trimming

#### DESCRIPTION

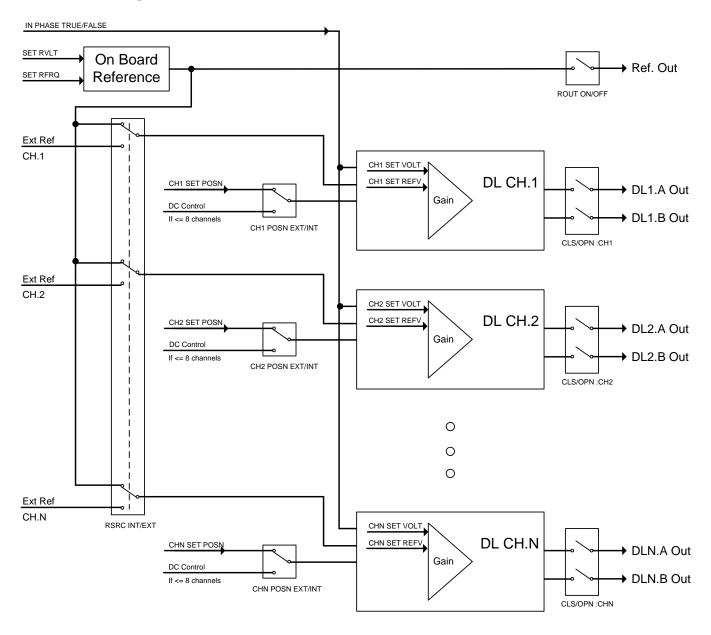

This single slot, message based VXIbus instrument can be populated with either one or two daughtercards. Each daughtercard can provide up to eight (8) LVDT/RVDT 3-wire with wraparound self test and an optional programmable excitation supply. Currently, a total of sixteen (12) 3-wire channels and an excitation supply can be provided within one single slot enclosure (see part number). An optional feature permits programming each output for either ratiometric or self-leveling (fixed) mode. In the ratiometric mode, the output voltage will vary directly/proportionately with the excitation voltage. In the self-leveling (or fixed) mode, the output voltage is programmed and remains constant regardless of excitation voltage. Standard/default is ratiometric. This card is a uniquely versatile instrument because each excitation input and output voltage is programmable. In addition, each channel may be programmed to be controlled by an external DC voltage (see part number).

09/11/12

SPECIFICATIONS: APPLIES TO EACH 8 CHANNEL DAUGHTERCARD

Number of Outputs: Eight. (maximum – see part number)

Output voltage (Va and Vb): 0-24 Vrms ±1% at no load. Transformer isolated.

Output voltage is programmable as % of full scale (FS) range

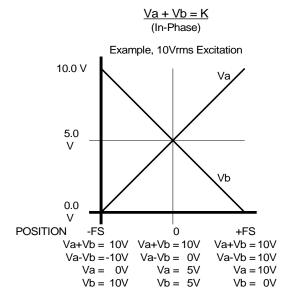

Output phasing: Either Va + Vb = K or Va - Vb = K, programmable

Accuracy:  $Va + Vb = K \pm 1\%$  or  $Va - Vb = K \pm 1\%$

Resolution: 16 bits (.001526% FS range)

Linearity: ±0.05% FS range (at 20 KHz, ±0.2% FS range)

Load: ±0.05% FS range (at 20 KHz, ±0.2% FS range)

3.5 ma. max. Outputs are short circuit protected.

Regulation: ±1% 10K ohms to no load

±2% with a 4K ohm load

Excitation: 2.0 to 28 Vrms; Programmable and Transformer isolated.

Excitation Current: 1.5 mA max. per channel @ 360 Hz.

Excitation Frequency: 360 Hz to 20 KHz. Output voltage will not vary more than ±1% over frequency.

Phase Shift: ±1.5° max

Ratiometric/Self-leveling: In the Ratiometric mode, the output voltage will vary directly with the excitation voltage.

In the Self-leveling mode, the programmed output voltage will remain constant even though the excitation varies. The Self-Leveling mode is optional. See part number.

Optional DC input: Differential. ±10 VDC or ±5 VDC. See part number. (System GND referenced).

Output Control: The Va and Vb outputs are controllable by either Internal or External commands.

In the External Mode, the Va and Vb outputs are controlled by an external analog signal. This differential input signal of  $\pm 10$  VDC or  $\pm 5$  VDC (see part number)

corresponds to 0 to 100% position.

Latency: Va to Vb latency: The differential latency between Va and Vb output changes as a

function of position change will be less than 500 nsec.

External Position to Output Latency: The time between an analog position input voltage

change and the corresponding Va & Vb output change will not exceed 200 µs.

Internal Position to Output Latency: The time between a position change commanded over the VXI bus for any given channel and the corresponding Va and Vb outputs

changing will not exceed 8 msec.

VXIbus Data rate: 2 megabytes/second

Temperature, operating: -10°C to +65°C

Temperature, storage: -40°C to +85°

Relative humidity: to 93% RH non-condensing Shock: Designed to meet 15G, 11 ms

Vibration: Designed to meet MIL-T-28800C for class V equipment.

Altitude, operating: 10,000 feet Altitude, non operating: 40,000 feet

Power Requirements: ±12 VDC at 600 mA

+5 VDC at 500 mA

Size: "C" size (13.386" x 9.187") with 1.2" pitch. (349mm x 234 mm) with 30 mm pitch

Weight: 4.3 lbs. (1.95 Kg)

Calibration intervals: No calibration is required.

Calibration intervals. No calibration is required.

Connectors: Mating connectors are not supplied.

**Excitation Supply** Optional. (See part number).

Voltage: 2.0-28 Vrms programmable (resolution 0.1 Vrms); Accuracy ±2%.

Frequency: 400 Hz to 10 KHz ±1% with 1 Hz resolution.

Regulation: 10% max. No load to full load.

Output power: 5 VA max. at 40° min. inductive.

**Power Requirements**

|                                                   | ±12Vdc                 | +5Vdc                  |

|---------------------------------------------------|------------------------|------------------------|

| Motherboard                                       | N/A                    | 660 mA                 |

| Daughter-card (handles up to four output modules) | 12 mA                  | 380 mA                 |

| Output Module (two channels)                      | 140 mA                 | 12 mA                  |

| Output LOADED – (adds per channel)                | 1.6 mA per 1 mA (load) | N/A                    |

| Excitation Module                                 | N/A                    | 110 mA                 |

| Excitation LOADED – (adds per channel)            | N/A                    | 275 mA per 1 VA (load) |

09/11/12

# PRINCIPAL OF OPERATION (LVDT)

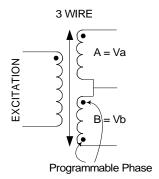

Typically the primary is excited by an AC source, causing a magnetic flux to be generated within the transducer. Voltages are induced in the two secondaries, with the magnitude varying with the position of the core. Usually, the secondaries are connected in series opposition, causing a net output voltage of zero when the core is at the electrical center. When the core is displaced in either direction from center the voltage increases linearly either in phase or out of phase with the excitation depending on the direction

# **Output Configuration**

POSITION = (Va-Vb) / (Va+Vb)

## **LVDT Coil Voltage vs. Position**

09/11/12

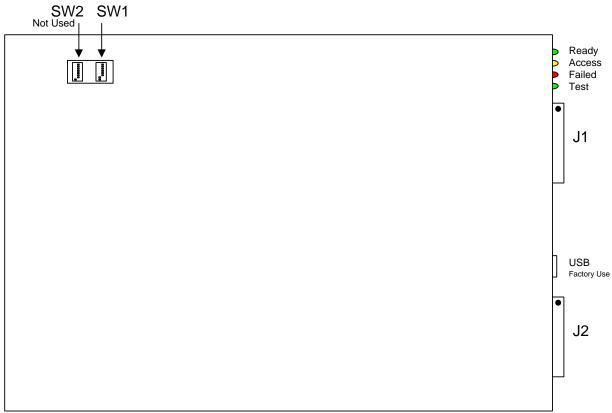

# **CARD ADDRESS**

Address Dip Switches 1 can each be configured for logical addresses 1 to 255, where OFF=1 and ON=0. LSB is position 1.

| Decimal   | Logical Address 128 (Default) | Logical Address 33 (Example) |

|-----------|-------------------------------|------------------------------|

| 1 (LSB)   | SW1, position 1=0 (ON)        | SW1, position 1=1 (OFF)      |

| 2         | SW1, position 2=0 (ON)        | SW1, position 2=0 (ON)       |

| 4         | SW1, position 3=0 (ON)        | SW1, position 3=0 (ON)       |

| 8         | SW1, position 4=0 (ON)        | SW1, position 4=0 (ON)       |

| 16        | SW1, position 5=0 (ON)        | SW1, position 5=0 (ON)       |

| 32        | SW1, position 6=0 (ON)        | SW1, position 6=1 (OFF)      |

| 64        | SW1, position 7=0 (ON)        | SW1, position 7=0 (ON)       |

| 128 (MSB) | SW1, position 8=1 (OFF)       | SW1, position 8=0 (ON)       |

65DL2 Bottom View

# FRONT PANEL STATUS INDICATORS

| Status Indicators | Function                                                                                            |

|-------------------|-----------------------------------------------------------------------------------------------------|

| READY             | Indicates that unit is ready to accept commands                                                     |

| ACCESS            | Indicator is lit when VXI bus controller sends or reads a message or status.                        |

| FAILED            | Lights on power-up and goes out after unit has passes system self-test. Stays lit if device has     |

|                   | failed Self-Test or Calibration. Indicator will also light in response to Controller SYSFAIL output |

| TEST              | Illuminates while Internal Self-Test is running, flashes while in Calibration.                      |

09/11/12

## **PROGRAMMING**

NOTE: To support output phase programming, native command

## IN\_PHASE [TRUE/FALSE]

where TRUE configures output for Va - Vb = K and FALSE configures output for Va + Vb = K was added.

The following sections define MATE/CIIL and SCPI formats with supporting examples.

# **Function Block Diagram**

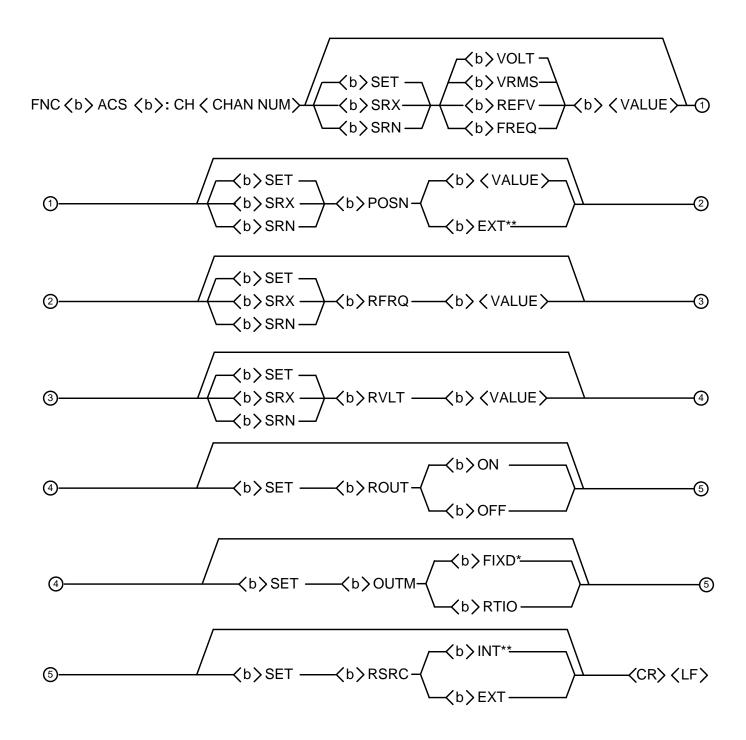

# MATE / CONTROL INTERMEDIATE INTERFACE LANGUAGE (CIIL) SYNTAX

Note: \* SET<b>OUTM<b>FIXD sets to Self Leveling Output. RTIO is for Ratiometric output.

\*\* SET<b>RSRC<b>INT sets ALL channels to internal reference source. Reference sources for individual channels cannot be set individually.

$CLS \langle b \rangle : CH \langle CHAN NUM \rangle \longrightarrow \langle CR \rangle \langle LF \rangle$

OPN \( b \rangle : CH \langle CHAN NUM \rangle \tag{CR} \langle (LF \rangle )

RST \( b \rangle ACS \( \chi \rangle CH \rangle CHAN NUM \rangle \tag{CR} \rangle LF \rangle

STA (CR) (LF)

IST (CR) (LF)

CNF (CR) (LF)

# RESPONSE TO STA

CH < CHAN NUM > where CHAN NUM = 0 TO n OR 00 TO n (where "n" equal maximum configured channels)

### **POWER ON or RESET Command Default Values**

RELAY(S) OPEN

VOLTAGE = 0.0 Volts

POSITION = 50 %

RSRC = EXT

REFV = 10 Vrms

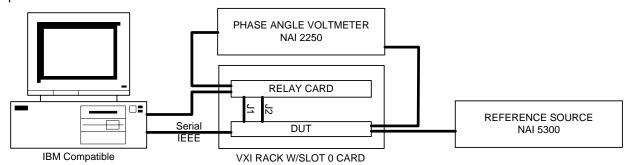

### **Error Reporting**

1. VXIbus Commands

Errors indicated by (ERR\*) bit in response register Errors reported in response to error query command

2. Operational or syntax errors

Error messages sent in response to serial message (STA)

## Response to (IST, CNF)

Open Isolation Relays

Input sequence of voltages to each cannel from internal source

Perform measurements

Compared with stored values

Max Self-test time = 60 seconds

09/11/12

#### **Data Field**

ASCII FLOATING POINT ±.DDDDDDDDDDE±DD

MANTISSA = 1 to 14 Digits EXPONENT = 1 or 2 Digits

ASCII DECIMAL ±DDDD.DDDDD

1 to 14 Digits

Decimal point at any position

ASCII INTEGER ±DDDDDDDD

1 to 15 Digits

ASCII SCIENTIFIC ±D.DDDDDDDDE±DD

MANTISSA = 1 to 14 Digits EXPONENT = 1 or 2 Digits

EXPONENT Range Limited -09 to +09

± Sign is Optional

No Sign = +

### **LVDT/RVDT Command Summary**

FNC (SET, SRX, SRN) set up instrument

CLS Close input path

OPN open input path

RST reset channel

STA report status

CNF perform confidence test IST perform built in test

IN\_PHASE Native command added to support output phase programming where

TRUE configures output for Va – Vb = K and FALSE configures output for Va + Vb = K

09/11/12

#### **Notation**

<CR> <LF> ASCII carriage return followed by ASCII line feed

<NOUN> ACS

<SET CODE> SET

SRX positive limit SRN negative limit

<MCHAR> VOLT

VRMS REFV FREQ POSN

RFRQ Added by NAI for Reference Programming

RVLT Added by NAI for Reference Programming

ROUT Added by NAI for Reference Programming

RSRC Added by NAI for Reference Programming

WHEN SET TO INTERNAL, DC INPUT IS DISABLED.

REFERENCE SOURCES TO INDIVIDUAL CHANNELS

CANNOT BE SET INDIVIDUALLY.

<CHAN NUM> 0 to 7,

or 00 to 07

<VALUE> See FNC Command Format

<MODIFIER> VOLT or VRMS Output Voltage

REFV Reference Voltage

FREQ Frequency

POSN Output Position, Center = 50%

#### **Command Format**

**FNC** instrument set-up

FNC<b><NOUN><b>:CH <CHAN NUM> [<b><SETCODE><b><MODIFIER><b><VALUE>]\*\*\*<CR><LF>

<NOUN> ACS (error msg) #1

<CHAN NUM> 0 to n, (where n = number of channels configured)

> or 00 to n (error msg) #4

<SETCODE> SRX Maximum value

**SET**

SRN Minimum value (error msg) #5

Voltage Span <MODIFIER> VOLT or VRMS

Expected Ref voltage input **REFV**

No effect **FREQ**

**POSN** (error msg) #7 Output Position

<VALUE> **REFV** 2 to 10 Vrms

**FREQ** 360 to 20,000 Hz **POSN** 0 to 100%.

or EXT (External)

**CLS** close isolation relay

CLS<b>:CH <CHAN NUM> <CR><LF>

**OPN** open isolation relay

OPN<b>:CH <CHAN NUM> <CR><LF>

RST<b>ACS<b>:CH <CHAN NUM> <CR><LF>

**STA** report status

STA <CR><LF>

Response

<b><CR><LF> Normal <error msg><CR><LF> Error

**IST** internal self test

IST <CR><LF>

**CNF** confidence

CNF<CR><LF> Confidence test requires up to 60 seconds before results are available

Optional field or structure field repeated as often as required

09/11/12

# **Error Messages**

- 1. "F07ACSnn (MOD): COMMAND ERROR";

- 2. "F07ACSnn (MOD): NOUN ERROR";

- 3. "F07ACSnn (MOD): MISSING CR";

- 4. "F07ACSnn (MOD): CHANNEL NUMBER ERROR";

- 5. "F07ACSnn (MOD): SET CODE ERROR";

- 6. "F07ACSnn (MOD): MCHAR ERROR";

- 7. "F07ACSnn (MOD): MODIFIER ERROR";

- 8. "F07ACSnn (MOD): VALUE ERROR";

- 9. "F07ACSnn (MOD): XPONENT RANGE ERROR";

- 10. "F07ACSnn (MOD): NO SPACE";

- 11. "F07ACSnn (MOD): BIT FAIL";

- 12. "F07ACSnn (MOD): MESSAGE OVERFLOW";

- 13. "F07ACSnn (MOD): MESSAGE SYNTAX ERROR";

Where nn is the channel number

09/11/12

## **Programming Examples**

Provided below are two programming examples. The 65DL2 is programmed using command strings of ASCII text, or command messages. These messages are displayed in quotes for convenience.

Example to set channel 0 for full 10 Vrms reference external, 10 Volts Line-Line and Full Scale (FS) position (100%)

SET RSRC EXT sets ALL channels to external references sources. Reference sources to individual channels cannot be set individually.

"FNC ACS :CH0 SET RSRC EXT"

"FNC ACS :CH0 SET REFV 10 SET VOLT 10 SET POSN 100"

"CLS:CH0"

"STA"

Read Device

Set Reference to External Program Output Configuration

Close Channel 0 Send Status Request

Expected Response is blank, or ASCII 32

Example to set channel 0 for 10 Vrms reference internal, 10 Volts Line-Line, 400Hz, and FS position (100%)

When setting Reference Source to Internal, DC Input control is disable or ignored.

SET RSRC INT sets ALL channels to internal references sources. Reference sources to individual channels cannot be set individually.

"FNC ACS :CH0 SET RSRC INT"

"FNC ACS :CH0 SET RVLT 10 SET RFRQ 400 SET POSN 100"

"FNC ACS :CH0 SET ROUT ON"

"CLS:CH0" "STA"

Read Device

Set Reference to Internal Program Output Configuration

Turn Reference ON Close Channel 0 Send Status Request

Expected Response is blank, or ASCII 32

Example to set channel 0 for 10 Vrms reference external, 10 Volts Line-Line and position to DC Input

SET RSRC EXT sets ALL channels to external references sources. Reference sources to individual channels cannot be set individually.

"FNC ACS :CH0 SET RSRC EXT"

"FNC ACS :CH0 SET REFV 10 SET VOLT 10 SET POSN EXT"

"CLS:CH0"

Read Device

"STA"

Set Reference to External

Program Output Configuration, Ext DC Input

Close Channel 0 Send Status Request

Expected Response is blank, or ASCII 32

User sets external DC Source to 10 volts (Option B)

Example to initiate and query confidence test

"CNF"

Wait or implement parallel task

Read Device

Initiate Confidence Test

09/11/12

Cage Code: 0VGU1

Confidence Test requires 60 second to complete

Poll DATA OUT READY Bit.

Expected Response is blank, or ASCII 32

North Atlantic Industries, Inc. 110 Wilbur Place, Bohemia, NY 11716

631.567.1100/631.567.1823 (fax) www.naii.com

65\_DL2\_A001\_Rev\_A3 Page 13 of 19

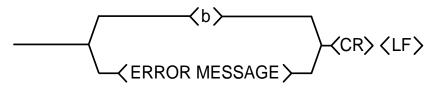

# **VERIFICATION TEST SET-UP**

This unit does not require field calibration because it is self calibrating. Use the following setup, or similar, to verify performance.

09/11/12

### **CONNECTORS:**

J1, \*J2: HDL78SLB Mate: HDT78PD with strain relief 745082-1

| **J3: | <b>DB25P</b> ; <b>Mate</b> : <b>DB25S</b> ; |

|-------|---------------------------------------------|

|       | J3                                          |

|     | J1                  |     |                     |  |

|-----|---------------------|-----|---------------------|--|

| Pin | Description         | Pin | Description         |  |

| 3   | Va                  | 11  | Va                  |  |

| 4   | Common Ch.0         | 12  | Common Ch.4         |  |

| 42  | Vb                  | 50  | Vb                  |  |

| 22  | Excitation HI       | 30  | Excitation HI       |  |

| 61  | Excitation Lo       | 69  | Excitation Lo       |  |

|     |                     |     |                     |  |

| 5   | Va                  | 13  | Va                  |  |

| 6   | Common Ch.1         | 14  | Common Ch.5         |  |

|     | Vb                  | 52  | Vb                  |  |

| 24  | Excitation HI       | 32  | Excitation HI       |  |

| 63  | Excitation Lo       | 71  | Excitation Lo       |  |

|     |                     |     |                     |  |

| 7   | Va                  | 15  | Va                  |  |

| 8   | Common Ch.2         | 16  | Common Ch.6         |  |

| 46  | Vb                  | 54  | Vb                  |  |

| 26  | Excitation HI       | 34  | Excitation HI       |  |

| 65  | Excitation Lo       | 73  | Excitation Lo       |  |

|     |                     |     |                     |  |

| 9   | Va                  | 17  | Va                  |  |

| 10  | Common Ch.3         | 18  | Common Ch.7         |  |

| 48  | Vb                  | 56  | Vb                  |  |

| 28  | Excitation HI       | 36  | Excitation HI       |  |

| 67  | Excitation Lo       | 75  | Excitation Lo       |  |

|     |                     |     |                     |  |

| 20  | Internal Exc.Hi Out | 59  | Internal Exc.Lo Out |  |

|     | J2                   |     |                      |  |

|-----|----------------------|-----|----------------------|--|

| Pin | Description          | Pin | Description          |  |

| 3   | Va                   | 11  | Va                   |  |

| 4   | Common Ch.0          | 12  | Common Ch.4          |  |

| 42  | Vb                   | 50  | Vb                   |  |

| 22  | Excitation HI        | 30  | Excitation HI        |  |

| 61  | Excitation Lo        | 69  | Excitation Lo        |  |

| 5   | Va                   | 13  | Va                   |  |

|     | Common Ch.1          | 14  | Common Ch.5          |  |

| 44  | Vb                   | 52  | Vb                   |  |

| 24  | Excitation HI        | 32  | Excitation HI        |  |

| 63  | Excitation Lo        | 71  | Excitation Lo        |  |

|     |                      |     |                      |  |

| 7   | Va                   | 15  | Va                   |  |

| 8   | Common Ch.2          | 16  | Common Ch.6          |  |

| 46  | Vb                   | 54  | Vb                   |  |

| 26  | Excitation HI        | 34  | Excitation HI        |  |

| 65  | Excitation Lo        | 73  | Excitation Lo        |  |

| 9   | Va                   | 17  | Va                   |  |

|     | Common Ch.3          | 18  | Common Ch.7          |  |

| 48  | Vb                   | 56  | Vb                   |  |

|     | Excitation HI        | 36  | Excitation HI        |  |

| 67  | Excitation Lo        | 75  | Excitation Lo        |  |

|     |                      |     |                      |  |

| 20  | Internal Exc. Hi Out | 59  | Internal Exc. Lo Out |  |

Pin Description DC Hi Ch. 0 DC Lo Ch. 0 DC Hi Ch. 1 DC Lo Ch. 1 DC Hi Ch. 2 DC Lo Ch. 2 6 DC Hi Ch. 3 8 DC Lo Ch. 3 DC Hi Ch. 4 10 DC Lo Ch. 4 DC Hi Ch. 5 11 DC Lo Ch. 5 12 DC Hi Ch. 6 23 DC Lo Ch. 6 24 DC Hi Ch. 7 25 DC Lo Ch. 7

For 12 channels units, 8 channels are on J1 and 4 channels are on J2 (channels 9 thru 12 are referenced on J2 as respective Ch0 thru Ch3).

DO NOT CONNECT TO ANY UNDESIGNATED PINS.

09/11/12

<sup>\*</sup>J2 is only supplied when 12 channels are specified

<sup>\*\*</sup> J3 is only supplied when external DC is specified (For 8 channel units only)

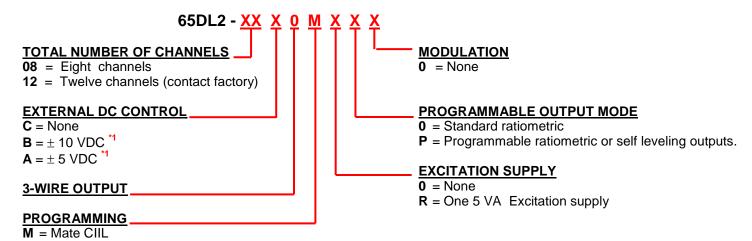

### **PART NUMBER DESIGNATION**

#### Notes:

09/11/12

<sup>&</sup>lt;sup>\*1</sup> Option available on 8 channel configuration only

# APPENDIX A - CE

# INFORMATION FOR UNITS SOLD WITHIN THE EUROPEAN UNION

#### **GENERAL**

Information contained within the following paragraphs supplements and in some cases supersedes information contained throughout this Manual. Where there is a conflict between information contained in these paragraphs and information contained elsewhere in the manual, these paragraphs take precedence for units sold within the European Union.

#### **CLASSIFICATION**

The 65 series model is defined for CATEGORY I installation and usage in a POLLUTION DEGREE 1 environment.

#### **INSTALLATION**

The 65 series model is designed for installation in a VXI standard card cage. Only the front panel is accessible to the OPERATOR during normal usage.

#### **SAFETY GROUNDING**

For safety from electrical shock and fire, the mounting surface (rear) of the front panel must be kept free of contamination and the unit must be mounted in a VXI card cage with the mounting screws properly tightened. The VXI card cage frame must be properly connected to a safety earth ground.

#### **IMPROPER USAGE**

If the equipment is installed or used in a manner not specified safety may be impaired. The equipment may not be used in CATEGORY II, III or IV installation.

#### **MAINTENANCE**

The OPERATOR only has access to the exterior of the unit. All maintenance, including any procedures that require removal of covers, must be referred to qualified maintenance personnel

#### **TECHNICAL ASSISTANCE**

Contact your local Sales Representative for any technical assistance. Alternatively, contact the Factory at:

North Atlantic Industries 110 Wilbur Place Bohemia, NY 11716 USA

Telephone: (631) 567-1100 Fax: (631) 567-1823 Web: www.naii.com

09/11/12

# **DECLARATION OF CONFORMITY**

We NORTH ATLANTIC INDUSTRIES, INC. 110 WILBUR PLACE, BOHEMIA, NY 11716-2416

declare under our sole responsibility that the following products

### 65 SERIES

To which this declaration relates is in conformity with the following standard(s) or other normative document(s):

EMISSIONS PER EN 61326:1997/A1:1998/A2:2001

CISPR16:1999 Class A, Conducted Emissions CISPR16:1999 Class A, Radiated Emissions

IEC 61000-3-2:2000 Harmonics IEC 61000-3-3:1994 Flicker

IMMUNITY PER EN 61326:1997/A1:1998/A2:2001

IEC 1000-4-2:1995 Electrostatic Discharge IEC 1000-4-3:1995 Radiated Immunity

IEC 1000-4-4:1995 EFT/Burst, Power and I/O Leads IEC 1000-4-5:1995 Surge Immunity, Power Leads

IEC 1000-4-6:1996 Conducted Immunity, Power and I/O Leads

IEC 1000-4-11:1994 Voltage Dips and Interrupts

SAFETY PER EN 61010-1:2001

IEC 61010-1:2001 Safety

Following the provisions of COUNCIL DIRECTIVE 89/336/EEC

2006/95/EC

Place Bohemia NY, USA (original on file)

(Signature)

Date 5/27/05 Rob Carillo (Full Name)

Quality Manager

(Position)

09/11/12

# **REVISION PAGE**

| Revision | Description of Change                                                                                                                                           | Engineer | Date     |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|

| 4.0      | Initial Release                                                                                                                                                 | GS       | 5/05/03  |

| 4.1      | Appends Output Voltage spec from $\pm 34$ to 0–24Vrms $\pm 1\%$ at no load. Added Card Address. Added Programming section to define 8 or 16 channel addressing. | GS       | 5/19/3   |

| 4.2      | Adds Programming Examples. Addes Assy Dwgs. Adds RSRC INT.                                                                                                      | GS       | 6/3/3    |

| 5.0      | Added two excitation supplies for 16 ch. Design; various clarifications                                                                                         | FH       | 12/17/03 |

| 5.1      | Clarified P/N designation                                                                                                                                       | FH       | 12/18/03 |

| 6.0      | native command IN_PHASE [TRUE/FALSE] added where TRUE configures output for Va – Vb = K and FALSE configures output for Va + Vb = K                             | GS       | 7/29/04  |

| 6.1      | Adds 12 channels                                                                                                                                                | GS       | 12/7/4   |

| 6.2      | Adds Function Block Diagram                                                                                                                                     | GS       | 3/2/5    |

| 6.3      | Update Function Block Diagram                                                                                                                                   | GS       | 3/3/5    |

| 6.4      | Adds OUTM for self leveling vs ratiometric output.                                                                                                              | GS       | 7/12/5   |

| 6.5      | CHANGED ADDRESS                                                                                                                                                 | DD       | 05/07/07 |

| Α        | Updated power requirements / Added Appendix A - CE addendum                                                                                                     | AS       | 05/15/08 |

| A1       | Agile-format / Added self-leveling mode description / Removed SW2 addressing references                                                                         | AS       | 05/19/08 |

| A2       | Release to Agile                                                                                                                                                | AS       | 05/29/08 |

| А3       | Clarified available part number configuration option(s) / limited to 12 CH max.                                                                                 | AS       | 09/11/12 |

09/11/12 Cage Code: 0VGU1